- 您现在的位置:买卖IC网 > Sheet目录1249 > TS-MAC-XM-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI-SPD XP

�� �

�

Lattice� Semiconductor�

�Core� Signal� Descriptions�

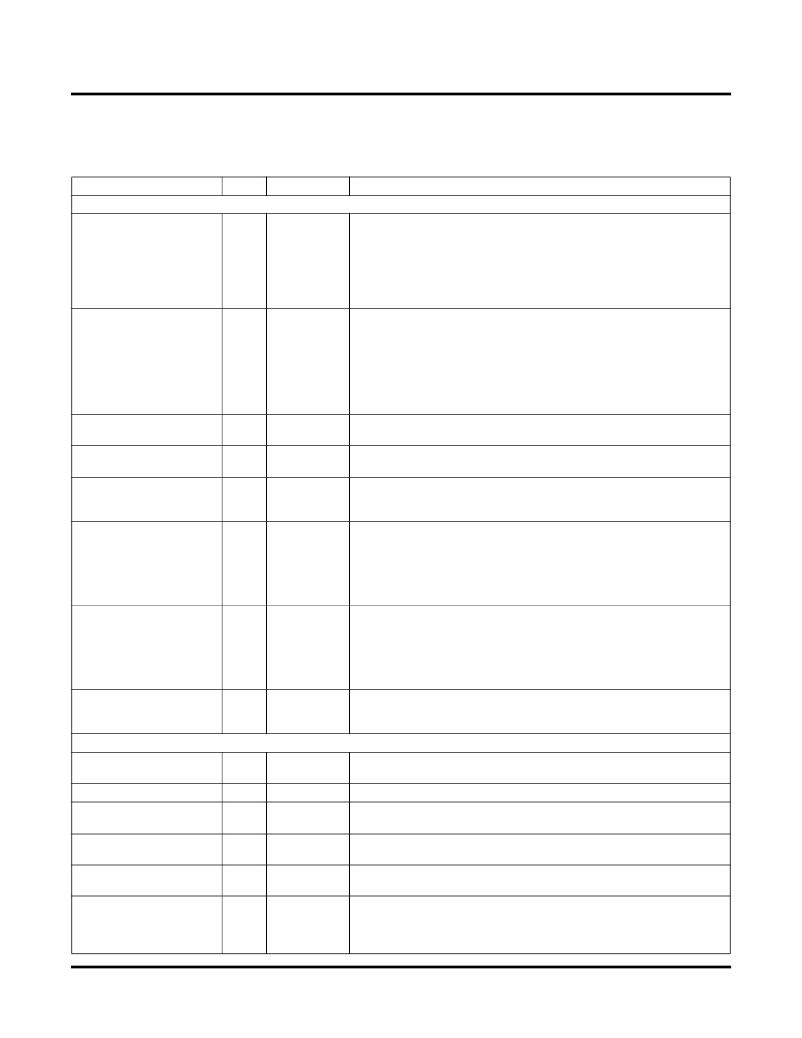

��Table� 2-1.� TSMAC� IP� Core� Input� and� Output� Signals�

�Functional� Description�

�Port� Name�

�Type�

�Active� State�

�Description�

�Clocks� and� Reset/Other�

�Receive� MAC� Application� Interface� Clock.� This� clock� is� used� by� the�

�client� application� and� MAC.� All� outputs� driven� by� the� Rx� MAC� on� the� cli-�

�ent� side� are� synchronous� to� this� clock.� This� clock’s� frequency� is� 125,12.5�

�rxmac_clk�

�Input�

�N/A�

�or� 1.25� MHz� depending� on� the� mode� 1G/100/10� respectively.�

�Note:� this� clock� can� be� viewed� as� a� “byte”� clock,� since� all� Rx� MAC� bytes�

�are� aligned� with� this� clock.� This� clock� is� derived� from� the� system� G/MII�

�rx_clk.� Always� 125� MHz� in� Easy� Connect� mode.�

�Transmit� MAC� Application� Interface� Clock� .� This� clock� is� used� by� the�

�client� application� and� MAC.� All� inputs� to� the� Tx� MAC� on� the� client� side�

�should� be� synchronous� to� this� clock.� This� clock’s� frequency� is� 125,12.5�

�txmac_clk�

�Input�

�N/A�

�or� 1.25� MHz� depending� on� the� mode� 1G/100/10� respectively.�

�Note:� this� clock� can� be� viewed� as� a� “byte”� clock,� since� all� Tx� MAC� bytes�

�should� be� aligned� with� this� clock.� This� clock� is� derived� from� the� system�

�sys_clk� or� tx_clk.� (1G� or� 10/100� respectively).� Always� 125� MHz� in� Easy�

�Connect� mode.�

�hclk�

�mdc�

�Input�

�Input�

�N/A�

�N/A�

�Host� Clock� .� This� is� the� Host� Bus� clock,� and� is� used� to� clock� the� Host�

�Bus� interface.�

�Management� Data� Clock� .� This� clock� is� used� only� when� the� Manage-�

�ment� Interface� module� is� implemented.�

�Reset� .� This� is� an� active� low� asynchronous� signal� that� resets� the� internal�

�reset_n�

�Input�

�Low�

�registers� and� internal� logic.� When� activated,� the� I/O� signals� are� driven� to�

�their� inactive� levels.�

�Tx� Clock� Enable� .� This� input� signal� is� a� clock� enable� used� only� in� the�

�SGMII� Easy� Connect� option.� The� SGMII_PCS� IP� core� drives� this� signal.�

�txmac_clk_en�

�Input�

�N/A�

�The� clock� enable� is� always� high� for� 1G� operation.� For� 100� Mbps� opera-�

�tion� the� clock� enable� is� asserted� high� once� every� ten� (125MHz)� clocks,�

�and� for� 10� Mbps� operation� the� clock� enable� is� asserted� high� once� every�

�hundred� (125MHz)� clocks.�

�Rx� Clock� Enable� .� This� input� signal� is� a� clock� enable� used� only� in� the�

�SGMII� Easy� Connect� option.� The� SGMII_PCS� IP� core� drives� this� signal.�

�rxmac_clk_en�

�Input�

�N/A�

�The� clock� enable� is� always� high� for� 1G� operation.� For� 100� Mbps� opera-�

�tion� the� clock� enable� is� asserted� high� once� every� ten� (125MHz)� clocks,�

�and� for� 10� Mbps� operation� the� clock� enable� is� asserted� high� once� every�

�hundred� (125MHz)� clocks.�

�CPU� Interface� 1G� Mode� Enabled� Indication� .� This� signal,� when� high,� is�

�cpu_if_gbit_en�

�Output�

�High�

�an� indication� from� the� CPU� interface� that� the� 1G� mode� is� enabled.� This�

�signal� reflects� the� state� of� bit� 0� of� the� MAC� mode� register.�

�Host� Interface�

�hcs_n�

�haddr[7:0]�

�hdatain[7:0]�

�hwrite_n�

�hread_n�

�Input�

�Input�

�Input�

�Input�

�Input�

�Low�

�N/A�

�N/A�

�Low�

�Low�

�Chip� Select� .� This� is� an� active� low� signal� used� to� select� the� core� for� reg-�

�ister� Read/Write� operations.�

�Address� .� This� selects� one� of� the� internal� core� registers.�

�Data� Bus� Input� .� The� CPU� writes� to� the� internal� registers� through� the�

�data� bus.�

�Host� Write� .� This� active� low� signal� is� used� to� write� data� to� the� selected�

�register.�

�Host� Read� .� This� active� low� signal� is� used� to� read� data� from� the� selected�

�register.�

�Ready� .� This� is� an� active� low� signal� used� to� indicate� the� end� of� transfer.�

�hready_n�

�Output�

�Low�

�For� write� operations,� hready_n� is� asserted� after� data� is� accepted� (writ-�

�ten).� For� read� operations� hready_n� is� asserted� after� data� on� the�

�hdataout� bus� is� ready� to� be� driven� out.�

�IPUG51_03.0,� December� 2010�

�14�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TS250-130F-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RB-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS600-170F-2

POLYSWITCH PTC RESET 0.17A T/R

TS600-200F-RA-B-0.5-2

POLYSWITCH PTC RESET 0.20A SMD

TS600-400F-2

POLYSWITCH PTC RESET 0.40A SMD

相关代理商/技术参数

TSMBG0505C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|100V V(BO) MAX|DO-215AA

TSMBG0506C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|110V V(BO) MAX|DO-214AA

TSMBG0507C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|145V V(BO) MAX|DO-214AA

TSMBG0509C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|185V V(BO) MAX|DO-215AA

TSMBG0510C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|200V V(BO) MAX|DO-214AA

TSMBG0511C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|210V V(BO) MAX|DO-214AA

TSMBG0512C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|215V V(BO) MAX|DO-214AA

TSMBG0514C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|250V V(BO) MAX|DO-214AA